从事PCB规划的都知道,假如没有一点高速方面的常识,那你就不是一个有经历的PCB规划工程师。以下是关于高速信号方面的一些常识,快来“拾贝”吧。

一、串行总线/并行总线

高速信号常见于各类串行总线与并行总线,只要你知道是什么总线,知道它跑多快,才干开端进行布线。

什么是串行总线、并行总线?从字面含义你就能知道个大约。串行便是数据是一位一位的发送,并行便是数据一组一组的发送。如下图所示:

并行传输最好的比方是存储芯片DDR,它是有一组数据线D0—D7,加DQS,DQM,这一组线是一同传输的,不管哪位发生过错,数据都不会正确的传送曩昔,只要从头传输。

并行数据由于是一组一组一同传的,每一位都必须是一同传输到位,不能说有一位能够迟到一点,因而一组线之间在PCB布线时就得等长。

串行数据就不相同,数据是一位一位的传,位与位之间是没有联络的。不过,串行数据虽说是一位一位的传,不必等长,但也并不是一根线,高速线一般都是走差分线,也便是一正一负两根线。这是为了进步抗干扰功能。

二、高带要害信号包地处理

高速信号线中如时钟钱,最好选用包地处理,并且包地每隔3000mil打一个过孔连接到地层。要害信号与其它线之间要满意3W规矩。如下图所示:

此外,在高速PCB规划中,时钟等要害的高速信号线,走线需求进行屏蔽处理,假如没有屏蔽或只屏蔽了部分,都会形成EMI的走漏。

三、焊盘对高速信号的影响

在PCB中,从规划的视点来看,一个过孔主要由两部分组成:中心的钻孔和钻孔周围的焊盘。焊盘对高速信号有影响,其影响相似器材的封装对器材的影响。详细的剖析是,信号从IC内出来今后,经过绑定线、管脚、封装外壳、焊盘、焊锡抵达传输线,这个过程中的一切关节都会影响信号的质量。

但实践剖析时,很难给出焊盘、焊锡加上管脚的详细参数。所以一般就用IBIS模型中的封装的参数将它们都归纳了,当然这样的剖析在较低的频率上能够接纳,但对於更高频率信号更高精度仿真就不行准确。现在的一个趋势是用IBIS的V-I、V-T曲线描绘Buffer特性,用SPICE模型描绘封装参数。

四、AC耦合电容

AC耦合电容的作用是供给直流偏压,滤除信号的直流重量,使信号关于0轴对称。为什么要在PCB板上高速信号上添加AC耦合电容,当然是有优点的,添加AC耦合电容能够使两级之间更好的通讯,能够改进噪声容限。要知道AC耦合电容一般是高速信号阻抗不接连的点,并且会导致信号边缘变得缓慢。

AC耦合电容典型通路

那AC耦合电容在PCB规划时需求留意什么呢?万变不离根底原理。AC耦合电容一般是高速信号阻抗不接连的点,环绕这个问题解决便是它规划上的留意点。比方AC耦合电容优化,比方高速板材的选取等等。

(图文收拾自网络)

想扩大和提高自己硬件方面的技术吗?想在职场上提高自己的竞争力吗?无妨从学习原理图规划开端。可在“腾讯讲堂”学习Orcad原理图规划实战课程:《4周经过VR学习原理图规划》噢。

毕业不慌,查厉来帮|爱企查携手西电学子深度体验品牌魅力

毕业不慌,查厉来帮|爱企查携手西电学子深度体验品牌魅力 史上最刺激的闪购,淘宝百亿补贴凌晨放大招,真梦里啥都有!

史上最刺激的闪购,淘宝百亿补贴凌晨放大招,真梦里啥都有! 技术与文化融合 芒果的AI全链路实践

技术与文化融合 芒果的AI全链路实践 全国人大代表刘宏志:推动数字乡村建设、激发乡村振兴“数智力量”

全国人大代表刘宏志:推动数字乡村建设、激发乡村振兴“数智力量” “千翼飞舞天际 5G闪耀广州”2023数字科技生态大会 11月10日中国·广州

“千翼飞舞天际 5G闪耀广州”2023数字科技生态大会 11月10日中国·广州 DR钻戒应急玫瑰活动在法国巴黎迅速蹿红 带火了七夕情人节

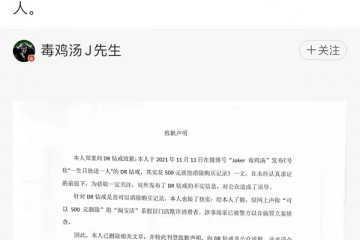

DR钻戒应急玫瑰活动在法国巴黎迅速蹿红 带火了七夕情人节 “DR钻戒可删除购买记录”谣言正式澄清 传谣者公开道歉

“DR钻戒可删除购买记录”谣言正式澄清 传谣者公开道歉 美国网件NETGEAR助力打造全屋网络覆盖利器,推出全新WiFi-6 三频AX6000

美国网件NETGEAR助力打造全屋网络覆盖利器,推出全新WiFi-6 三频AX6000