IEEE IEDM大会上,台积电官方披露了5nm工艺的最新进展,给出了很多确凿数据,看起来非常的欢天喜地。

台积电

5nm将是台积电的又一个重要工艺节点,分为N5、N5P两个版别,前者比较于N7 7nm工艺功能提高15%、功耗下降30%,后者在前者基础上持续功能提高7%、功耗下降15%。

台积电5nm将运用第五代FinFET晶体管技能,EUV极紫外光刻技能也扩展到10多个光刻层,全体晶体管密度提高84%7nm是每平方毫米9627万个晶体管,5nm就将是每平方毫米1.771亿个晶体管。

台积电称5nm工艺现在正处于危险试产阶段,测验芯片的良品率均匀已达80%,最高可超越90%,不过这些芯片都相对很简单,假如放在杂乱的移动和桌面芯片上,良品率还做不到这么高,但详细数据未公开。

详细来说,台积电5nm工艺的测验芯片有两种,一是256Mb SRAM,单元面积包含25000平方纳米的高电流版别、21000平方纳米的高密度版别,后者号称是迄今最小的,总面积5.376平方毫米。

二是归纳了SRAM、CPU/GPU逻辑单元、IO单元的,面积占比分别为30%、60%、10%,总面积估量大约17.92平方毫米。

依照这个面积核算,一块300mm晶圆应该能生产出3252颗芯片,良品率80%,那么无缺的芯片至少是2602个,缺点率1.271个每平方厘米。

当然,现代高功能芯片面积都相当大,比方麒麟990 5G达到了113.31平方毫米。

依照一颗芯片100平方毫米核算,1.271个每平方厘米的缺点意味着良品率为32%,看着不高但关于危险试产阶段的工艺来说仍是彻底合格的,满足合作伙伴进行前期测验与评价。

别的,AMD Zen2架构每颗芯片(八中心)的面积约为10.35×7.37=76.28平方毫米,对应良品率便是41%。

台积电还发布了5nm工艺下CPU、GPU芯片的电压、频率对应联系,CPU经过测验的最低值是0.7V、1.5GHz,最高能做到1.2V 3.25GHz,GPU则是最低0.65V 0.66GHz、最高1.2V 1.43GHz。当然这都是开始成果,后续必定还会大大提高。

台积电估计,5nm工艺将在2020年上半年投入大规模量产,相关芯片产品将在2020年晚些时候连续上台,苹果A14、华为麒麟1000系列、AMD Zen4架构四代锐龙都是妥妥的了,仅仅听说初期产能会被苹果和华为根本吃光。

毕业不慌,查厉来帮|爱企查携手西电学子深度体验品牌魅力

毕业不慌,查厉来帮|爱企查携手西电学子深度体验品牌魅力 史上最刺激的闪购,淘宝百亿补贴凌晨放大招,真梦里啥都有!

史上最刺激的闪购,淘宝百亿补贴凌晨放大招,真梦里啥都有! 技术与文化融合 芒果的AI全链路实践

技术与文化融合 芒果的AI全链路实践 全国人大代表刘宏志:推动数字乡村建设、激发乡村振兴“数智力量”

全国人大代表刘宏志:推动数字乡村建设、激发乡村振兴“数智力量” “千翼飞舞天际 5G闪耀广州”2023数字科技生态大会 11月10日中国·广州

“千翼飞舞天际 5G闪耀广州”2023数字科技生态大会 11月10日中国·广州 DR钻戒应急玫瑰活动在法国巴黎迅速蹿红 带火了七夕情人节

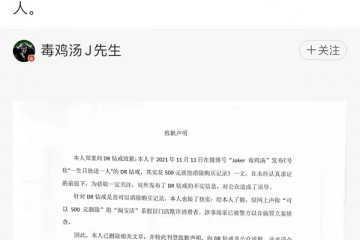

DR钻戒应急玫瑰活动在法国巴黎迅速蹿红 带火了七夕情人节 “DR钻戒可删除购买记录”谣言正式澄清 传谣者公开道歉

“DR钻戒可删除购买记录”谣言正式澄清 传谣者公开道歉 美国网件NETGEAR助力打造全屋网络覆盖利器,推出全新WiFi-6 三频AX6000

美国网件NETGEAR助力打造全屋网络覆盖利器,推出全新WiFi-6 三频AX6000